Advanced Design System 2011.01

Feburary 2011 Advanced Design System Quick Start

## © Agilent Technologies, Inc. 2000-2011

5301 Stevens Creek Blvd., Santa Clara, CA 95052 USA

No part of this documentation may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Agilent Technologies, Inc. as governed by United States and international copyright laws.

## Acknowledgments

Mentor Graphics is a trademark of Mentor Graphics Corporation in the U.S. and other countries. Mentor products and processes are registered trademarks of Mentor Graphics Corporation. \* Calibre is a trademark of Mentor Graphics Corporation in the US and other countries. "Microsoft®, Windows®, MS Windows®, Windows NT®, Windows 2000® and Windows Internet Explorer® are U.S. registered trademarks of Microsoft Corporation. Pentium® is a U.S. registered trademark of Intel Corporation. PostScript® and Acrobat® are trademarks of Adobe Systems Incorporated. UNIX® is a registered trademark of the Open Group. Oracle and Java and registered trademarks of Oracle and/or its affiliates. Other names may be trademarks of their respective owners. SystemC® is a registered trademark of Open SystemC Initiative, Inc. in the United States and other countries and is used with permission. MATLAB® is a U.S. registered trademark of The Math Works, Inc.. HiSIM2 source code, and all copyrights, trade secrets or other intellectual property rights in and to the source code in its entirety, is owned by Hiroshima University and STARC. FLEXIm is a trademark of Globetrotter Software, Incorporated. Layout Boolean Engine by Klaas Holwerda, v1.7 http://www.xs4all.nl/~kholwerd/bool.html . FreeType Project, Copyright (c) 1996-1999 by David Turner, Robert Wilhelm, and Werner Lemberg. QuestAgent search engine (c) 2000-2002, JObjects. Motif is a trademark of the Open Software Foundation. Netscape is a trademark of Netscape Communications Corporation. Netscape Portable Runtime (NSPR), Copyright (c) 1998-2003 The Mozilla Organization. A copy of the Mozilla Public License is at <a href="http://www.mozilla.org/MPL/">http://www.mozilla.org/MPL/</a> . FFTW, The Fastest Fourier Transform in the West, Copyright (c) 1997-1999 Massachusetts Institute of Technology. All rights reserved.

The following third-party libraries are used by the NlogN Momentum solver:

"This program includes Metis 4.0, Copyright © 1998, Regents of the University of Minnesota", <u>http://www.cs.umn.edu/~metis</u>, METIS was written by George Karypis (karypis@cs.umn.edu).

Intel@ Math Kernel Library, http://www.intel.com/software/products/mkl

SuperLU\_MT version 2.0 - Copyright © 2003, The Regents of the University of California, through Lawrence Berkeley National Laboratory (subject to receipt of any required approvals from U.S. Dept. of Energy). All rights reserved. SuperLU Disclaimer: THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

7-zip - 7-Zip Copyright: Copyright (C) 1999-2009 Igor Pavlov. Licenses for files are: 7z.dll: GNU LGPL + unRAR restriction, All other files: GNU LGPL. 7-zip License: This library

Advanced Design System 2011.01 - Advanced Design System Quick Start is free software; you can redistribute it and/or modify it under the terms of the GNU Lesser General Public License as published by the Free Software Foundation; either version 2.1 of the License, or (at your option) any later version. This library is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU Lesser General Public License for more details. You should have received a copy of the GNU Lesser General Public License along with this library; if not, write to the Free Software Foundation, Inc., 59 Temple Place, Suite 330, Boston, MA 02111-1307 USA. unRAR copyright: The decompression engine for RAR archives was developed using source code of unRAR program.All copyrights to original unRAR code are owned by Alexander Roshal. unRAR License: The unRAR sources cannot be used to re-create the RAR compression algorithm, which is proprietary. Distribution of modified unRAR sources in separate form or as a part of other software is permitted, provided that it is clearly stated in the documentation and source comments that the code may not be used to develop a RAR (WinRAR) compatible archiver. 7-zip Availability: http://www.7-zip.org/

AMD Version 2.2 - AMD Notice: The AMD code was modified. Used by permission. AMD copyright: AMD Version 2.2, Copyright © 2007 by Timothy A. Davis, Patrick R. Amestoy, and Iain S. Duff. All Rights Reserved. AMD License: Your use or distribution of AMD or any modified version of AMD implies that you agree to this License. This library is free software; you can redistribute it and/or modify it under the terms of the GNU Lesser General Public License as published by the Free Software Foundation; either version 2.1 of the License, or (at your option) any later version. This library is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU Lesser General Public License for more details. You should have received a copy of the GNU Lesser General Public License along with this library; if not, write to the Free Software Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA Permission is hereby granted to use or copy this program under the terms of the GNU LGPL, provided that the Copyright, this License, and the Availability of the original version is retained on all copies. User documentation of any code that uses this code or any modified version of this code must cite the Copyright, this License, the Availability note, and "Used by permission." Permission to modify the code and to distribute modified code is granted, provided the Copyright, this License, and the Availability note are retained, and a notice that the code was modified is included. AMD Availability: http://www.cise.ufl.edu/research/sparse/amd

UMFPACK 5.0.2 - UMFPACK Notice: The UMFPACK code was modified. Used by permission. UMFPACK Copyright: UMFPACK Copyright © 1995-2006 by Timothy A. Davis. All Rights Reserved. UMFPACK License: Your use or distribution of UMFPACK or any modified version of UMFPACK implies that you agree to this License. This library is free software; you can redistribute it and/or modify it under the terms of the GNU Lesser General Public License as published by the Free Software Foundation; either version 2.1 of the License, or (at your option) any later version. This library is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU Lesser General Public License for more details. You should have received a copy of the GNU Lesser General Public License along with this library; if not, write to the Free Software Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA Permission is hereby granted to use or copy this program under the terms of the GNU LGPL, provided that the Copyright, this License, and the Availability of the original version is retained on all copies. User documentation of any code that uses this code or any modified version of this code must cite the Copyright, this License, the Availability note, and "Used by permission." Permission to modify the code and to distribute modified code is granted, provided the Copyright, this License, and the Availability note are retained, and a notice that the code was modified is included. UMFPACK Availability: http://www.cise.ufl.edu/research/sparse/umfpack UMFPACK (including versions 2.2.1 and earlier, in FORTRAN) is available at

<u>http://www.cise.ufl.edu/research/sparse</u> . MA38 is available in the Harwell Subroutine Library. This version of UMFPACK includes a modified form of COLAMD Version 2.0, originally released on Jan. 31, 2000, also available at

<u>http://www.cise.ufl.edu/research/sparse</u> . COLAMD V2.0 is also incorporated as a built-in function in MATLAB version 6.1, by The MathWorks, Inc. <u>http://www.mathworks.com</u> . COLAMD V1.0 appears as a column-preordering in SuperLU (SuperLU is available at <u>http://www.netlib.org</u> ). UMFPACK v4.0 is a built-in routine in MATLAB 6.5. UMFPACK v4.3 is a built-in routine in MATLAB 7.1.

Qt Version 4.6.3 - Qt Notice: The Qt code was modified. Used by permission. Qt copyright: Qt Version 4.6.3, Copyright (c) 2010 by Nokia Corporation. All Rights Reserved. Qt License: Your use or distribution of Qt or any modified version of Qt implies that you agree to this License. This library is free software; you can redistribute it and/or modify it under the

terms of the GNU Lesser General Public License as published by the Free Software Foundation; either version 2.1 of the License, or (at your option) any later version. This library is distributed in the hope that it will be useful,

but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU Lesser General Public License for more details. You should have received a copy of the GNU Lesser General Public License along with this library; if not, write to the Free Software Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA Permission is hereby granted to use or copy this program under the terms of the GNU LGPL, provided that the Copyright, this License, and the Availability of the original version is retained on all copies.User

documentation of any code that uses this code or any modified version of this code must cite the Copyright, this License, the Availability note, and "Used by permission." Permission to modify the code and to distribute modified code is granted, provided the Copyright, this License, and the Availability note are retained, and a notice that the code was modified is included. Qt Availability: http://www.gtsoftware.com/downloads Patches

Applied to Qt can be found in the installation at:

\$HPEESOF\_DIR/prod/licenses/thirdparty/qt/patches. You may also contact Brian Buchanan at Agilent Inc. at brian\_buchanan@agilent.com for more information.

The HiSIM\_HV source code, and all copyrights, trade secrets or other intellectual property rights in and to the source code, is owned by Hiroshima University and/or STARC.

**Errata** The ADS product may contain references to "HP" or "HPEESOF" such as in file names and directory names. The business entity formerly known as "HP EEsof" is now part of Agilent Technologies and is known as "Agilent EEsof". To avoid broken functionality and to maintain backward compatibility for our customers, we did not change all the names and labels that contain "HP" or "HPEESOF" references.

**Warranty** The material contained in this document is provided "as is", and is subject to being changed, without notice, in future editions. Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied, with regard to this documentation and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein. Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with these terms, the warranty terms in the separate agreement shall control.

**Technology Licenses** The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license. Portions of this product include the SystemC software licensed under Open Source terms, which are available for download at <a href="http://systemc.org/">http://systemc.org/</a>. This software is

Advanced Design System 2011.01 - Advanced Design System Quick Start redistributed by Agilent. The Contributors of the SystemC software provide this software "as is" and offer no warranty of any kind, express or implied, including without limitation warranties or conditions or title and non-infringement, and implied warranties or conditions merchantability and fitness for a particular purpose. Contributors shall not be liable for any damages of any kind including without limitation direct, indirect, special, incidental and consequential damages, such as lost profits. Any provisions that differ from this disclaimer are offered by Agilent only.

**Restricted Rights Legend** U.S. Government Restricted Rights. Software and technical data rights granted to the federal government include only those rights customarily provided to end user customers. Agilent provides this customary commercial license in Software and technical data pursuant to FAR 12.211 (Technical Data) and 12.212 (Computer Software) and, for the Department of Defense, DFARS 252.227-7015 (Technical Data - Commercial Items) and DFARS 227.7202-3 (Rights in Commercial Computer Software or Computer Software Documentation).

| ADS Design Environment                               | 8  |

|------------------------------------------------------|----|

| ADS Main Window                                      | 8  |

| Workspace View Options                               | 9  |

| Design Windows                                       | 14 |

| Substrate Editor                                     | 15 |

| Data Display Window                                  | 15 |

| Manage ADS AEL Addons                                | 15 |

| Command Line Window (for AEL Commands)               | 17 |

| Component Palette                                    | 19 |

| Moving Toolbars (PC Only)                            | 19 |

| Simulation                                           |    |

| Setting Preferences for Miscellaneous Options        | 21 |

| Using Workspace                                      | 23 |

| Working in Workspaces                                | 24 |

| Creating a Workspace                                 | 24 |

| Opening a Workspace                                  | 27 |

| Deleting a Workspace                                 | 27 |

| Renaming a Workspace                                 |    |

| Archiving a Workspace                                | 28 |

| Unarchiving a Workspace                              | 28 |

| Opening an Example Workspace                         | 29 |

| Finding an Example Workspace or Design               | 29 |

| Closing a Workspace                                  | 31 |

| Exiting from ADS                                     | 31 |

| Using Libraries                                      | 32 |

| Using Designs                                        | 39 |

| Creating Designs                                     | 39 |

| Opening Design                                       | 41 |

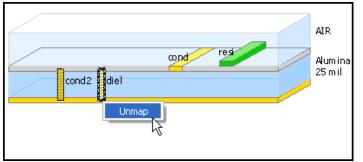

| Substrates in EM Simulation                          | 42 |

| Substrate Editor                                     | 42 |

| Creating a Substrate                                 | 43 |

| Opening a Substrate                                  | 43 |

| Saving a Substrate                                   | 44 |

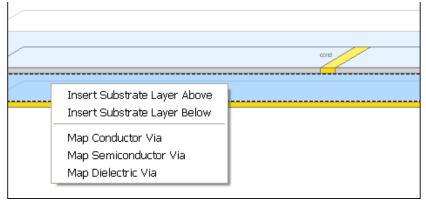

| Inserting, Moving, and Deleting Items                | 44 |

| Editing Substrate Properties                         | 46 |

| Verifying Substrate Definition                       | 49 |

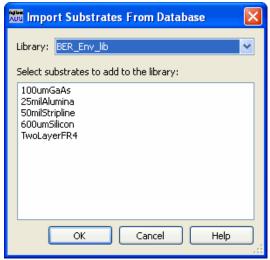

| Importing a Substrate                                | 49 |

| Simulating Designs                                   | 51 |

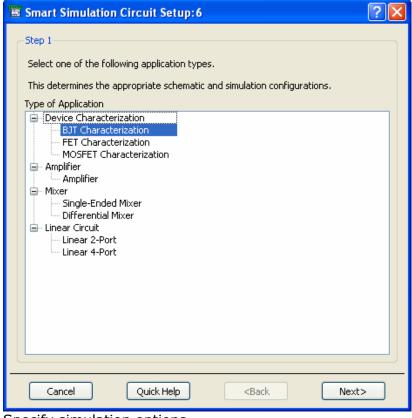

| Simulation Wizard                                    | 52 |

| Signal Processing Simulation                         | 54 |

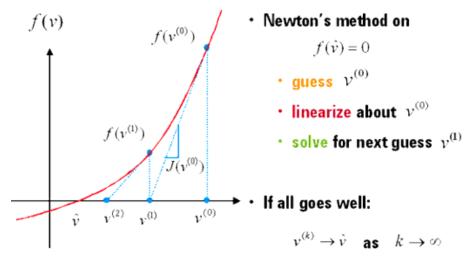

| Analog/RF Simulation and Convergence                 | 55 |

| Common Circuit Simulation Methods                    | 57 |

| Using Continuation Methods                           | 59 |

| Momentum Simulation, Optimization, and Visualization | 60 |

| Instrument Connectivity                              | 61 |

| Simulation Controllers                               | 61 |

| Optimization & Statistical Design Controllers        | 61 |

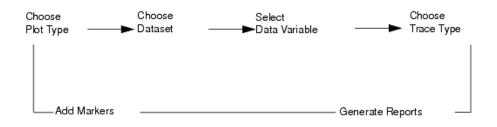

| Analyzing Results                                    | 63 |

| Creating Data Displays                               | 63 |

| Viewing Results                                      | 64 |

| Using Functions                                      | 66 |

| Inputs and Outputs                                   | 67 |

| Importing and Exporting Design                       | 67 |

| Supported Data Transfer Format                       | 70 |

| Simulation and Optimization Controllers              | 72 |

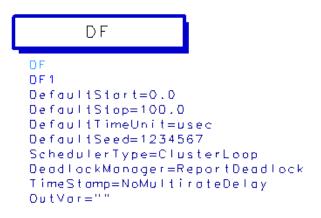

| Data Flow Simulation Controller                      | 72 |

| DC Simulation Controller                             | 72 |

| AC Simulation Controller               | 73 |

|----------------------------------------|----|

| S-Parameter Simulation Controller      | 73 |

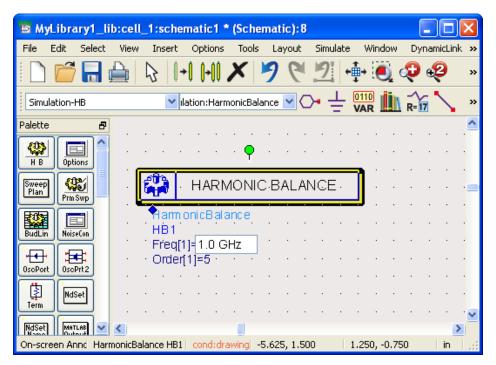

| Harmonic Balance Simulation Controller | 74 |

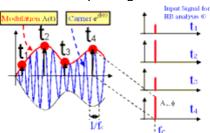

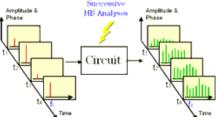

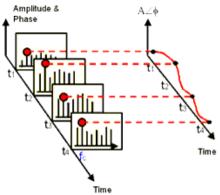

| Circuit Envelope Simulation Controller | 77 |

| LSSP Simulation Controller             | 81 |

| XDB Simulation Controller              | 81 |

| Transient/Conv. Simulation Controller  | 82 |

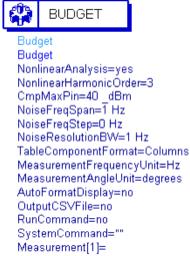

| RF Budget Controller                   | 89 |

| Nominal Optimization Controller        | 89 |

| Monte Carlo Controller                 | 90 |

| Yield Analysis Controller              | 90 |

| Yield Optimization Controller          | 91 |

| Design of Experiments Controller       | 91 |

|                                        |    |

# **ADS Design Environment**

This section provides a quick introduction to the ADS Design Environment. The ADS design environment has multiple windows. The ADS Main Window (also referred to as Main Window) is your first interface to start using the ADS. This window allows you to access all the features supported by ADS.

# **ADS Main Window**

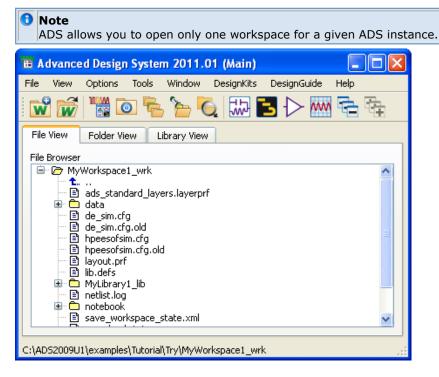

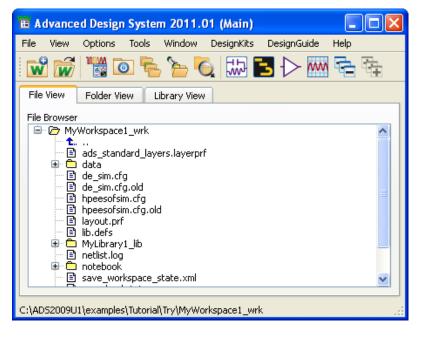

The ADS Main Window enables you to create and manage ADS workspaces. A *workspace* is an organizer where you can group everything about a design within— such as libraries, technology, schematic, layout, simulation data, and Momentum data. The entire ADS user interface and simulation operates within a currently opened workspace. The **File View** page of the Main window allows you to traverse to your existing workspaces (located in the *default* folder). To open any of these workspaces, select and right-click on the workspace and choose **Open Workspace** or double-click on the selected workspace.

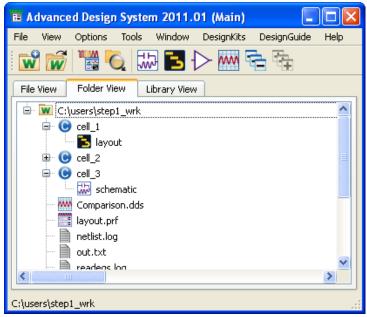

Once a workspace is open, ADS automatically switches to the **Folder View** page where it displays all the contents of that workspace, and you can start designing schematic or layout, or perform tasks like simulation of the designs already created. From ADS Main Window, see the **File** menu options for more extensive workspace management commands.

### 📵 Note

After opening a workspace, the toolbar buttons displayed in **File View** and **Folder View** or **Library View** are different.

From the ADS Main window you can:

- Create or open a workspace, cell, library, view, substrate, and hierarchy policy

- Upgrade a project to a workspace (for ADS 2009 Update 1 and earlier users)

- Quickly open an example workspace (**File > Open > Example**)

- Archive (File > Archive Workspace) or Un-Archive (File > Unarchive Workspace or Project) workspace

- Set program preferences (**Option > Preferences**)

- Change toolbar configuration and keyboard shortcuts (Tools > Hot Key/Toolbar Configuration)

- Manage Technology associated with a workspace (**Options > Technology**)

- Record and play macro (from **Tools** menu option)

- Load AEL files/commands from the Command line (Tools > Command Line)

- Launch the text editor

- Open data display and Schematic window

- Show/Hide all windows

- Display all types of files and open as required using the context-sensitive menu

# **Workspace View Options**

From the ADS Main window, the view options are provided for a workspace in three different tabs.

These tabs show a different view of the workspace and the loaded libraries. Changes made in any of these tabs (such as renaming or deleting a file or view) will affect all three tabs.

# **File View**

In the File View, you can:

- Browse to other directories (similar to previous releases)

- See the actual files that are stored in the file system

- View special characters in cell names shown in parenthesis (special characters are used by OpenAccess for cross-platform support). This improves readability.

## **Folder View**

In the Folder View, you can:

• Create virtual folders to group related files (similar to previous releases)

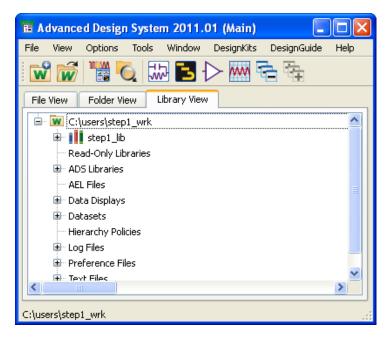

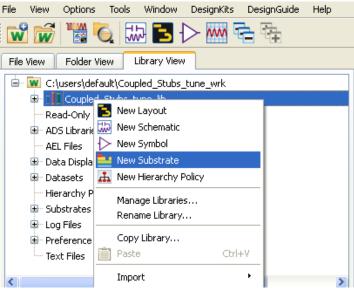

# **Library View**

In the Library View, you can:

- · View the system organization of a workspace

- Find files by type

🖯 Note

Some of the Main window menu and toolbar items will change as you move between Folder View and File View. For details, see <u>Context Menu</u>.

From ADS Main Window, you can create a new workspace or upgrade your ADS project (created using ADS 2009 Update 1 or earlier versions) to workspace. For more details on creating a new workspace, see *Using Workspace* (adstour). If you have been using ADS

2009 Update 1 or earlier version, you will have to upgrade you ADS Project to ADS Workspace. For more details, see ADS Project Upgrade to ADS Workspace (oaqkref).

Note To know more about ADS workspaces, see Workspace (oaqkref).

# **Context Menu**

In Folder View each Cell, Library, Workspace, and file contain the context menu. These menus can be different for different file types and workspace. The table below lists the different context menus associated with design or file type. To access these menus, right-click on a file, design, workspace, or folder in the Folder View.

### File Types/Folders and Associated Context Menus

| Context Menus                          | Designs | Data<br>Display<br>(*.dds) | Datasets<br>(*.ds) | Workspace<br>and Folders |   | Preferences<br>(*.prf) | Layers<br>(*.lay) | Text<br>(*.txt) |

|----------------------------------------|---------|----------------------------|--------------------|--------------------------|---|------------------------|-------------------|-----------------|

| Open (Schematic,<br>Layout, or Symbol) | х       |                            |                    |                          |   |                        |                   |                 |

| Open Data Display                      |         | Х                          |                    |                          |   |                        |                   |                 |

| Open in Text Editor                    |         |                            |                    |                          | Х | Х                      | Х                 | Х               |

| Create New Folder                      |         |                            |                    | X                        |   |                        |                   |                 |

| <u>Load</u>                            |         |                            |                    |                          | Х |                        |                   |                 |

| Сору                                   | Х       | Х                          | Х                  | X <sup>†</sup>           | Х | Х                      | Х                 | Х               |

| Paste                                  |         |                            |                    | X                        |   |                        |                   |                 |

| Copy Files                             | Х       | Х                          | Х                  | X                        | Х | х                      | Х                 | Х               |

| Rename                                 | Х       | Х                          | Х                  | Х                        | Х | Х                      | Х                 | Х               |

| <u>Delete</u>                          | Х       | Х                          | Х                  | X <sup>++</sup>          | Х | Х                      | X                 | Х               |

| Filter View                            | Х       | Х                          | Х                  | X                        | Х | х                      | Х                 | Х               |

| Expand Items in<br>Folder              | Х       | Х                          | x                  | X                        | х | Х                      | x                 | Х               |

| Collapse Items in<br>Folder            | Х       | Х                          | x                  | X                        | х | Х                      | x                 | X               |

<sup>+</sup> Group copy of files in folder. Invokes the copy/rename wizard.

<sup>++</sup> Group delete of files in folder.

## **Create New Folder**

You can create folders in the Folder View using the context menu of any existing Workspace or folder.

To create a new folder from your Folder View,

- 1. Right-click on the Workspace or any folder and choose **New Folder** from the pop-up menu. The New Folder dialog box appears.

- 2. Enter a name for the new folder and click **OK** to create the folder or click **Cancel** to abort the operation.

## **Dragging and Dropping Folders and Designs**

The Folder View enables you to simply drag and drop a folder or design to a new

location/folder.

To drag and drop a folder or design,

- 1. Locate the folder or design that you want to move in the Folder View.

- 2. Click and drag folder or design to the new location/folder.

- 3. Release the mouse button to drop the folder or design in the new location/folder. When you release the mouse button, pop-up menu appears with following options:

- Move Tree Item: It allows you to drop the folder or design into the new location/folder.

- Copy Files: For information on Copy Files, see Copying Files.

## Loading AEL Files

You can load Application Extension Language (AEL) files directly from the context menu of any AEL file (\*.ael) in your Workspace.

To load an AEL file from your Folder View,

- 1. Ensure the .ael file that you want to load is displayed in your Folder View. If you cannot see the .ael file in your Folder View, you may need to set the <u>Filter View</u> option to include AEL files.

- 2. From your Folder View, right-click the .ael file that you want to load.

- 3. Choose **Load**, the AEL file is automatically loaded (executed).

Only files in the top directory of your Workspace will show up in the Folder View. For more information on the AEL files, refer to the *AEL* (ael) documentation.

## Copy and Paste Files

The *Copy* context menu enables you to copy file(s) in the buffer. You can then use the *Paste* context menu to place a copy of the file(s). If you are pasting the file(s) into the same Workspace then the Copy Files dialog box will open and allow you to specify a different name for the file(s).

## **Rename Files**

The *Rename* context menu enables you to rename a file that you have selected. Simply right-click a file that you want to rename and choose Rename. Modify the filename and press Enter to change the name. If you are renaming a design, all other designs that reference this design will be modified to use the new design name.

## **Copying Files**

The Copy Files dialog box enables you to manage copy operations of a single file or multiple selected files. The Copy Files operation is accessible through the *Context Menus* and will also appear if you attempt to drag and drop a file into another Workspace or folder enabling you to select either *Move File* or *Copy File*.

To copy a file or group of files,

- 1. Select the file(s) in your Folder View.

- 2. Right-click and choose *Copy Files* from the context menu. The Copy Files dialog box appears.

- 3. Select *Include hierarchy* if you want to include sub-networks of the selected designs that you are going to copy.

<sup>🖯</sup> Note

- Set your Destination by selecting a Workspace or Directory from the drop-down list, or click **Browse** to access a different Workspace or directory.

- 5. Click **Choose Folder** to select a different folder.

- 6. Use the *Auto Rename Rule* options to automatically rename your copied file(s) using specific criteria. The available options include:

- Filename plus number incremented <filename>\_v<number> Copies the existing filename(s) and appends an \_v plus a version number to the filename(s).

- Filename plus maximum number incremented <filename>\_v<number> Copies the existing filename(s) and appends an \_v and the highest version number in all current filename(s), plus one, to the new filename(s).

- Number incremented plus filename v<number>\_<filename> Copies the existing filename(s) and pre-pends a v plus a version number and an underscore to the filename(s).

- Maximum number incremented plus filename v<number>\_<filename> Copies the existing filename(s) and pre-pends a v and the highest version number in all current filename(s), plus one, and an underscore to the new filename(s).

- None Copies the file(s) using the existing filename(s).

- 7. After setting the Auto Rename Rule, the new name(s) can be modified manually in the *New Filename* field.

- 8. Verify that your new names are correct. The existing names (current files) will appear in the *Current Filename* field, while the new names (file copies) are displayed in the *New Filename* field.

- 9. Click **OK** to copy the file(s) and dismiss the dialog box or click **Cancel** to abort the operation.

## **Delete Files**

You can delete one or more files in the Folder View by right-clicking the filename(s) and choosing the *Delete* context menu. If you are deleting designs that are referenced by other designs, you will be shown the other designs and asked if you are sure to delete the designs.

To delete a file or group of files,

- 1. Right-click the file that you want to delete in the Folder View.

- 2. If you want to delete more than one file, hold down the **Shift** key to select a group of files and/or use the **Ctrl** key to select multiple individual files.

- 3. Choose the *Delete* context menu.

- 4. Click **Yes** to confirm deletion. The files are deleted from disk and memory.

## **Filter View**

The View Options dialog box enables you to specify the file types that you want display or hide in the ADS Folder View. To start the View Options dialog box and change the display options:

- 1. Start ADS and open or create a workspace.

- 2. Select Folder View, if not selected.

- 3. Right-click anywhere in the blank space and select *Filter View...* menu option to open the View Options dialog box.

|    | 🗉 View Options 🛛 ? 🔀                          |  |  |  |  |  |

|----|-----------------------------------------------|--|--|--|--|--|

|    | Cham bhann file burne ir bha 111adhanna 16ann |  |  |  |  |  |

|    | Show these file types in the Workspace View:  |  |  |  |  |  |

|    | AEL                                           |  |  |  |  |  |

|    | 🗹 Data Display                                |  |  |  |  |  |

|    | 🗹 Dataset                                     |  |  |  |  |  |

|    | 🗹 Cell                                        |  |  |  |  |  |

|    | Hierarchy Policy                              |  |  |  |  |  |

|    | Substrates                                    |  |  |  |  |  |

|    | 🗹 Layer                                       |  |  |  |  |  |

|    | 🗹 Log                                         |  |  |  |  |  |

|    | Preference                                    |  |  |  |  |  |

| 2  | 🗹 Text                                        |  |  |  |  |  |

| 3. |                                               |  |  |  |  |  |

|    | OK Cancel                                     |  |  |  |  |  |

|    |                                               |  |  |  |  |  |

- 4. Enable (select) the file types that you want to appear in the Folder View.

- 5. Disable (deselect) the file types that you do not want to appear in the Folder View.

- 6. Click **OK** to accept the changes and dismiss the View Options dialog box, or click **Cancel** to abort.

The available file types are:

- Ael AEL files (\*.ael) in the Workspace's top directory.

- Data Display Data Display files (\*.dds) in the Workspace's top directory.

- Dataset dataset files (\*.ds) in the data directory.

- Cell Cells

- Hierarchy Policy The hierarchy policy

- Substrates Substrates

- *Layers* layers files (\*.lay) in the Workspace's top directory.

- Log Log files

- Preferences preferences files (\*.prf) in the Workspace's top directory.

- Text text files (\*.txt) in the Workspace's top directory.

# **Design Windows**

ADS allows you to create different design types such as, schematic, symbol, and layout. A design can consist of a number of schematics and layouts embedded as subnetworks within a single design. All designs in a workspace can be displayed and opened directly from the ADS Main window.

A design window is where you create and edit all your designs. You can resize and move these windows in the workspace. You can enlarge one window to fill the entire workspace and you can shrink each window to an icon. ADS supports following design windows:

- 1. Schematic Window (adstour)

- 2. Symbol Window (adstour)

- 3. Layout Window (adstour)

For more details, see Using Designs (adstour)

# **Substrate Editor**

For details, see *Substrate Editor* (adstour)

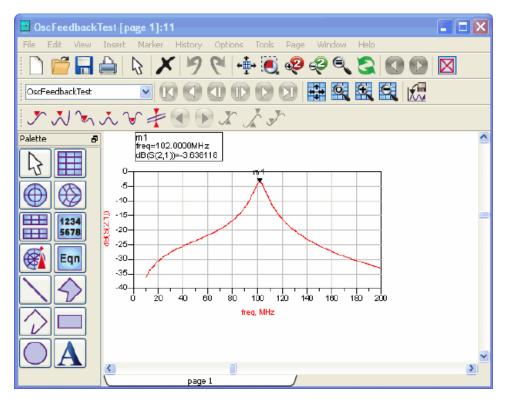

# **Data Display Window**

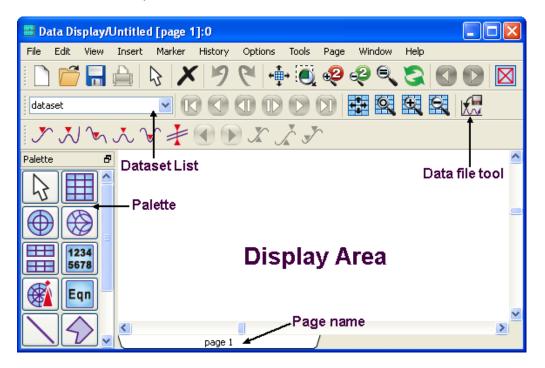

The Data Display window (see figure below) enables you to view and analyze the data generated by simulation, as well as data that has been imported from other sources, such as a network analyzer or CITIfile.

Data Display window allows you to:

- Display data in a variety of plots and formats.

- Create plots with more than two axes.

- Add markers to traces to read specific data points.

- Write mathematical equations to perform complex operations on data, and display the results.

- Add text and drawing objects to enhance your documentation.

- Edit plot titles and axis labels, equations, text, drawing objects, and column headings in lists.

For more details, see *Data Display Basics* (data)

# Manage ADS AEL Addons

Manage ADS AEL Addons dialog box can be used to add customized functionality to ADS. The customized AEL files can be loaded at ADS startup. Also, the AEL Addons can be enabled or disabled. ADS installer provides some example of **ADS Installation Addons**. These examples must be enabled by you.

Advanced Design System 2011.01 - Advanced Design System Quick Start Addons can be added at three access levels:

- SITE level: This information is stored at \$HPEESOF\_DIR/custom/config/eesof\_addons.xml.

- **INSTALL level:** This informationn is stored at \$HPEESOF\_DIR/config/eesof\_addons.xml.

- USER level: This information is stored at \$HOME/hpeesof/config/eesof\_addons.xml.

#### 🖯 Note

Hand-editing of the USER level *eesof\_addons.xml* file is not recommended, the USER level file is managed and controlled by the Manage ADS AEL Addons dialog.

The SITE and INSTALL access level addons are displayed in the dialog box only if the addons are available, and not otherwise.

### 🖯 Note

A Site Administrator can provide their own custom AEL addons for their site by adding their own customized eesof\_addons.xml file to the SITE level SHPEESOF\_DIR/custom/config/eesof\_addons.xml

location. The easiest way to do this is for the administrator to set up their user ael addons, then copy their

user file to the site level.

To start th Manage ADS AEL Addons dialog box, from ADS Main window select **Tools > Manage ADS AEL addons**.

| ī | B Manage ADS AEL Addons                                                                                                                                                                                                                        |             | ×                                                                                                                                                                                               |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Name                                                                                                                                                                                                                                           | Enabled     | Addon File location                                                                                                                                                                             |

|   | ADS Installation Addons     Layout Command Line Editor (Beta)     PCB Library Import Tools - Mentor     PCB Library Import Tools - Cadence     PCB Library Import Tools - All Vendors     PCB Library User Tools - All Vendors     User Addons | <b>&gt;</b> | \$HPEESOF_DIR\layout_command_line_e(<br>\$HPEESOF_DIR\lms\LMSStartup.atf<br>\$HPEESOF_DIR\lms\LMSCDNSStartup.atf<br>\$HPEESOF_DIR\lms\LMSStartupAll.atf<br>\$HPEESOF_DIR\lms\LMSUserStartup.atf |

|   | save_project_state.atf                                                                                                                                                                                                                         |             | C:\ADS2009U1\examples\Tutorial\BER_Ei                                                                                                                                                           |

|   | Add User ADS AEL Addon Remove User ADS                                                                                                                                                                                                         | AEL Addor   | n<br>Close Help                                                                                                                                                                                 |

# Add ADS AEL Addon

Follow the steps below to add a new user AEL addon and enable the same:

1. From the Manage ADS AEL Addons dialog box, click **Add User ADS AEL Addon**.

| 🖥 Add ADS AEL Addon 🛛 🔀                 |

|-----------------------------------------|

| Path                                    |

| C:\users\default Browse                 |

| Name                                    |

| (The name to associated with the Addon) |

| Enable Addon to load at ADS Startup     |

| Enable at ADS startup.                  |

|                                         |

| OK Cancel Help                          |

- 2. In the Add ADS AEL Addon window, type the system filepath location to the custom .ael or .atf AEL file into *Path*. You can also click **Browse** to select your custom AEL or ATF file.

- 3. Type a unique identifier name for your custom user AEL addon into *Name*.

- 4. Check the *Enable at ADS startup* option to enable loading of AEL file (selected in previous step) every time ADS starts.

- 5. Click **OK** to dismiss the window.

## **Remove ADS AEL Addon**

Follow the steps below to remove an user AEL addon:

- 1. From the Manage ADS AEL Addons dialog box, select the user addon you want to delete.

- 2. Click Remove User ADS AEL Addon.

- 3. From the confirmation message window, click **Yes** to remove.

# **Enable ADS AEL Addon**

To enable any AEL addon, you must check the *Enabled* option for the functionality that needs to be enabled.

- 1. From the Manage ADS AEL Addons dialog box, select the addon you want to enable.

- 2. Check the *Enabled* check box.

- 3. From the confirmation message window, click **Yes** to enable. By enabling an addon, it loads the corresponding AEL/ATF file when ADS starts.

## **Disable ADS AEL Addon**

To disable any addon, you must un-check the *Enabled* option for the functionality that needs to be disabled.

- 1. From the Manage ADS AEL Addons dialog box, select the addon you want to disable.

- 2. Un-check the \_Enabled" check box.

- 3. From the confirmation message window, click **Yes** to disable. You must restart ADS to disable the functionality.

# **Command Line Window (for AEL Commands)**

The *AEL* (ael) commands that are issued in response to your activity in the Main window and the design windows are displayed in the Command Line dialog box. This command summary is updated continuously as you work. You can view this summary any time and you can issue previously executed commands from this list.

To execute the AEL commands:

1. From the Main window, choose **Tools > Command Line** to open the Command Line window.

| 🕂 Command Line      | [ Session file: C | :\DOCUME~1\r | ajejain\ 🔀    |

|---------------------|-------------------|--------------|---------------|

| Command History     |                   |              |               |

|                     |                   |              |               |

|                     |                   |              |               |

|                     |                   |              |               |

|                     |                   |              |               |

| Command >>          |                   |              | Save Favorite |

|                     |                   | ~            |               |

| Current Vocabulary: | CmdOp             |              | Del Favorite  |

| Apply               | Clear History     | Cancel       | Help          |

Type the command(s) in the *Command* >> field and click **Apply** (or press **Enter** key) after each command to execute the same. As you execute commands, the corresponding AEL functions are displayed.

## **Current Vocabulary**

The Current Vocabulary option in command line window provides an option to select the AEL vocabulary in which you want the typed/selected AEL command to be executed in. *ComOp* is the default command. To change the vocabulary, click on the button provided next to the *Current Vocabulary* field. You can select the **Show Inheritance** option to see the inheritance hierarchy of AEL vocabularies available in ADS.

| 😃 Choose a Vocabulary 🔀                                                                                      |

|--------------------------------------------------------------------------------------------------------------|

| Vocabularies<br>AEL<br>CmdOp:AEL<br>SimCmd:CmdOp:AEL<br>RulesCmd:AEL<br>IFFCmd:CmdOp:AEL<br>Show Inheritance |

| Ok Cancel                                                                                                    |

For more information on AEL Vocabularies, see Introduction to AEL (ael).

#### 0 Notes

- 1. All commands entered in the *Command* >> field must be in AEL format.

- 2. You can also select a previously typed command from the list and press **Enter** key or click **Apply** to execute.

- 3. For configuration details on using AEL, refer to the *AEL* (ael) documentation. For layout artwork and usage, refer to the *Layout Library* (layout) documentation.

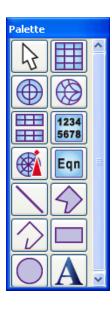

# **Component Palette**

Different design windows and other windows has a Component Palette which contains buttons that provide a quick method of placing items to create your design. This palette is available in:

- 1. Schematic Window

- 2. Data Display (DDS) Window

- 3. Symbol Window

- 4. Layout Window

**Component Palette in DDS Window**

#### 📀 Hint

All the palette items can also be placed through the Library. While some items are only available through the Library.

# Moving Toolbars (PC Only)

The toolbars can be repositioned anywhere on the screen. You can move them away from the window and use them like floating palettes or you can dock them along the window's edges.

### Hint

When the title bar of a toolbar is visible, positioning your pointer within the title bar for the drag operation simplifies the docking process. If a title bar is not visible, move the toolbar away from the window's edge and release; when it is not docked, a title bar appears.

To float a toolbar away from the window:

- 1. Place the cursor on left edge of the toolbar.

- 2. Drag the toolbar to the desired location and release. When you release the toolbar, a title bar appears at the top of it.

To dock a toolbar on a window border:

- 1. Place the cursor on left edge of the toolbar.

- 2. Drag the toolbar toward the desired window border and notice that the ghost image of the toolbar changes as needed to fit in a vertical or horizontal space.

- 3. When the ghost image reflects the proper orientation, release the mouse button and refine the toolbar's position by dragging as necessary.

To re-attach a toolbar near the top of the window:

- 1. Place the cursor on left edge of the toolbar.

- 2. Drag the toolbar toward the top of the window and when your pointer is overlapping the menu bar, or another toolbar, release.

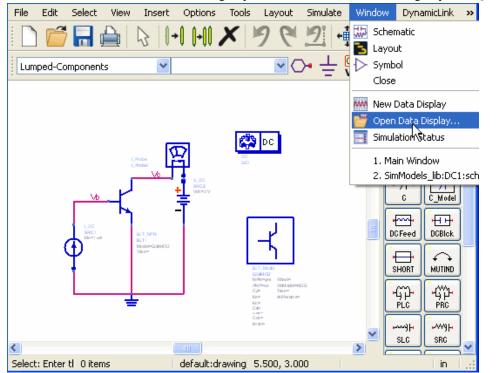

# Simulation

ADS allows you to create your own circuits which you can simulate using simulators provided to simulate the circuits and RF systems designed for specific objectives. You must have a valid ADS License to use these simulators.

There are different templates available to facilitate setting up common simulations. The simulation instrument components provide a method for symbolically connecting your circuit to an instrument. You connect your design to components that represent various instruments and run the simulation. Each simulation output generated with these simulators has a unique id.

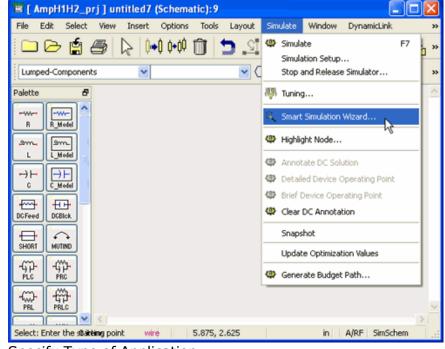

There are several ways to launch a simulation from the Schematic Window:

- Press the F7 key on your keyboard.

- Click the Simulate icon 🥮 on the toolbar.

- Choose **Simulate > Simulate**.

- Click **Simulate** from the Simulation Setup dialog box.

- 1. Choose **Simulate > Simulation Setup** to open the Simulation Setup dialog box.

| MyLibrary_lib:ce                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | II_1:schematic (Schematic):1                               |                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------|

| File Edit Select Vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ew Insert Options Tools Layout Simulate Window DynamicLink | »                                     |

| 🗋 📁 🔒                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Image: Simulate simulation Setup     F7                    | . »                                   |

| Lumped-Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Simulation Variables Setup<br>Hierarchy Explorer           | 🏩 🔋                                   |

| Palette 🗗                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Stop and Release Simulator                                 | 11 🛆                                  |

| B B Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                            | · · ·<br>· ·                          |

| L L Model I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Optimize Update Optimization Values                        | · · · · · · · · · · · · · · · · · · · |

| H H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | + Smart Simulation Wizard                                  |                                       |

| C C_Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                            | · · 📋                                 |

| DCFeed DCBlok                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Annotate DC Solution                                       |                                       |

| SHORT MUTIND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Brief Device Operating Point                               | · ·<br>· ·                            |

| -<br>-<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>μ<br>-<br>-<br>μ<br>-<br>-<br>μ<br>-<br>-<br>μ<br>-<br>-<br>-<br>μ<br>-<br>-<br>-<br>μ<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | Clear DC Annotation                                        | · · ·                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Generate Netlist                                           | · · · · · · · · · · · · · · · · · · · |

| Si 0 items                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IC_pin1_marker:c 3.625, 2.500 Generate Budget Path         | 1.1                                   |

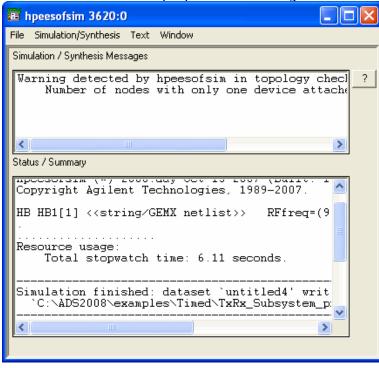

When the simulation begins, a status and error message window appears where you can see the simulation status and all the messages. Once the simulation is complete, **Simulation finished** message is displayed at the bottom of the window confirming that the simulation has run successfully. The location of the dataset where the simulation data is saved is also noted.

| hpeesofsim 29:15                                                                                                                                                                                               |               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| File Simulation/Synthesis Text Window                                                                                                                                                                          |               |

| Simulation / Synthesis Messages                                                                                                                                                                                |               |

| Warning detected by hpeesofsim during TRAN analysis 'Tranl'.<br>Component 'SNP1.CMP1':<br>No ImpMaxFreq is given, and maximum source bandwidth is ze                                                           | ro.           |

| Status / Summary                                                                                                                                                                                               |               |

|                                                                                                                                                                                                                | <b>^</b>      |

| Resource usage:                                                                                                                                                                                                | atic> time=(0 |

| <pre>TRAN Tran1[1] <convolutionbasics_2006u1_lib:d1_sparmodeluse:schem pre="" resource="" seconds.<="" stopwatch="" time="1.84" total="" usage:=""></convolutionbasics_2006u1_lib:d1_sparmodeluse:schem></pre> | atic> time=(0 |

| Resource usage:                                                                                                                                                                                                | atic> time=(0 |

| Resource usage:<br>Total stopwatch time = 1.84 seconds.<br>Simulation finished: dataset `d1_SparModelUse' written in:                                                                                          | atic> time=(0 |

For more details, see Simulating Designs (adstour) and Simulation Basics (cktsim).

# **Setting Preferences for Miscellaneous Options**

You can set preferences that affect you throughout the ADS design environment using the Main Preferences dialog box. To open the **Main Preferences** dialog box choose **Options > Preferences...** from the Main window.

Advanced Design System 2011.01 - Advanced Design System Quick Start To change any of these settings:

- 1. Change any or all options as desired.

- 2. Click **OK**. All changes take effect immediately, except as mentioned in the description below.

| 🕫 Main Preference                       |                                                             |  |  |

|-----------------------------------------|-------------------------------------------------------------|--|--|

| ✓ Warning bell                          | Enable Physical Connectivity Engine<br>(PCE) in new layouts |  |  |

| 🗹 Error bell                            | File Extensions                                             |  |  |

| 🗹 Large toolbar bitmap                  | Workspace Extension: _wrk                                   |  |  |

| Enable the Getting Started Dialog Box   | Wire Thickness                                              |  |  |

| Schematic Wizard                        | <ul> <li>Thin</li> <li>Medium</li> </ul>                    |  |  |

| Save all designs when simulation starts | O Thick                                                     |  |  |

| ✓ Save workspace state on exit          | External Text Editor<br>write.exe                           |  |  |

| OK Cancel Help                          |                                                             |  |  |

- **Warning Bell** The system beeps anytime you receive a pop-up window with a warning message.

- **Error Bell** The system beeps anytime you receive a pop-up window with an error message.

- Large Toolbar Bitmap A set of large bitmaps is placed on the toolbar. Turn this option off to place a set of small bitmaps on the toolbar (better for monitors with lower screen resolution). This change will be evident in any subsequently opened windows. To see the change take effect in a currently open window, open the Hot Key/Toolbar Configuration dialog box, click the Toolbar tab, and click **OK**.

- Enable the Getting Started Dialog Box The Getting Started dialog box is started at ADS startup.

- Schematic Wizard The system automatically launches the Schematic Wizard when a new design is created.

- Save all designs when simulation starts Save all the modified designs before launching the simulation.

- Save Workspace State on Exit The setup of the Workspace you are exiting is saved, including all design windows. The group of windows, and their positions on the screen, are restored the next time you open the Workspace.

- Enable Physical Connectivity Engine (PCE) in new layout Enables layout connectivity features. For more information, refer to *Physical Connectivity Engine* (usrguide)). See also the section on *Disabling Layout Connectivity Features* (usrguide) to understand the consequences of disabling the Physical Connectivity Engine.

- File Extensions

- 1. **Workspace Extension** The extension you want appended to workspace names, to clearly identify them as workspace (default is wrk).

- 2. **Library Extension** The extension you want appended to library names, to clearly identify them as library (default is lib).

- **Wire Thickness** The thickness (Thin, Medium, Thick) of all wires drawn in a Schematic window.

- External Text Editor Specifies the text editor to be launched when you choose Tools > Text Editor in the Main window.

# **Using Workspace**

Advanced Design System (ADS) uses the Workspace to organize and store the data generated when you create, simulate, and analyze designs. An ADS Workspace includes libraries, simulation data, data display files, and other related files.

A Workspace contains: